# Nano-probing and EBIC/EBAC

### Dr. Navid Asadi

#### Physical Inspection and AttacKs on ElectronicS (PHIKS)

Presented by: Nitin Varshney

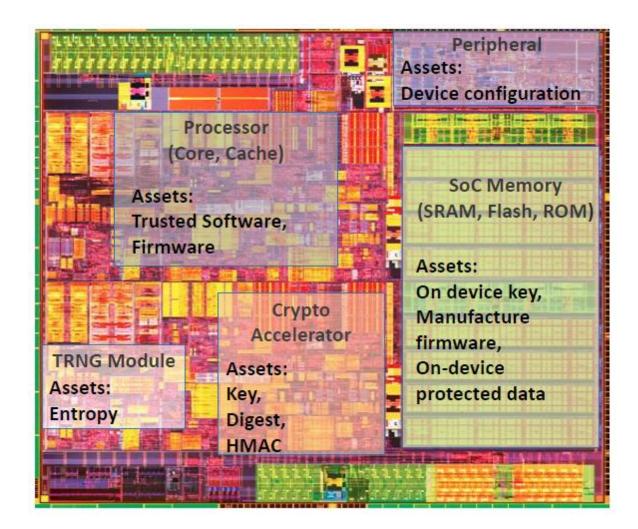

### **Critical Assets in SoCs**

**<u>Asset</u>**: A resource of value worth protecting from an adversary

#### Examples:

Research

- On-device keys (developer/OEM)

- Device configuration /defeaturing

- Manufacturer firmware

- Application software

- On-device sensitive data

- Communication credentials

- Random number or entropy

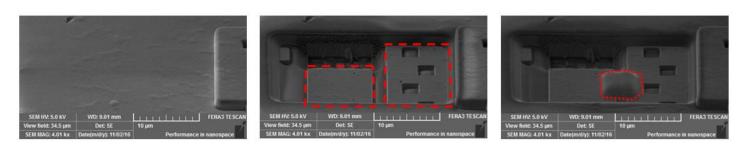

### Rise of Invasive attacks

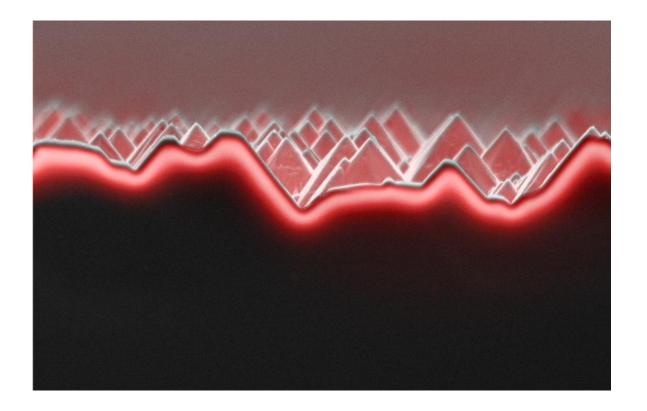

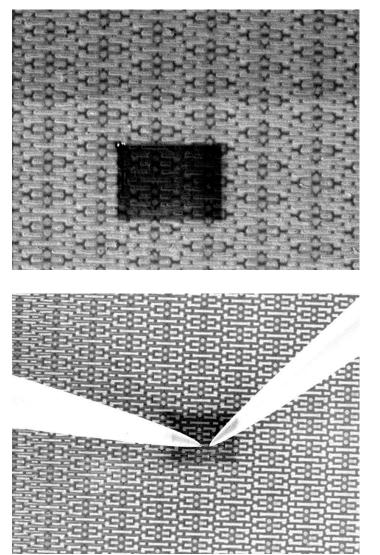

Pre-FIB surface

FIB milling to expose adjacent interconnects

FIB deposition to short adjacent interconnects

#### Focused Ion Beam (FIB)

• A powerful tool commonly used in the development, manufacturing, and editing of ICs

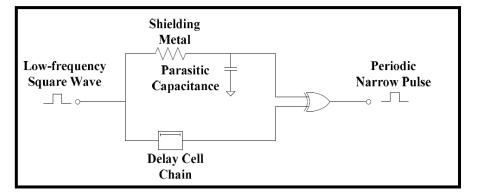

#### **Micro-probing / editing Attack**

- Probing at signal wires to extract security sensitive information

- Front-side attack and back-side attack

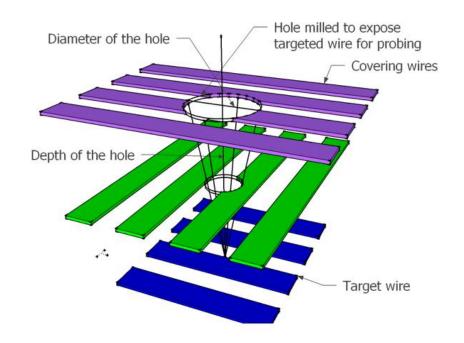

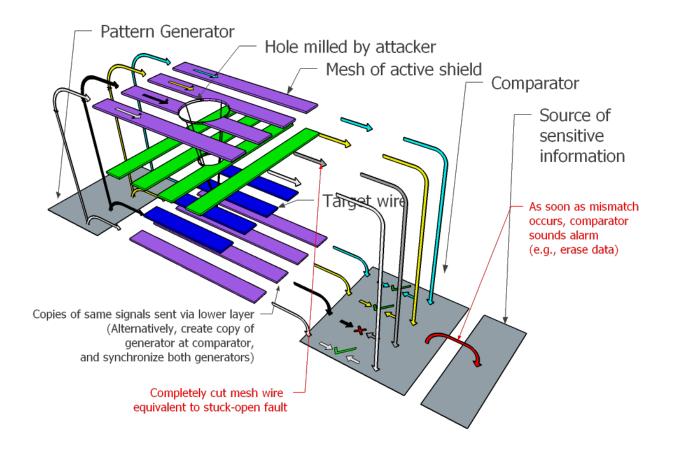

### **Active Shields**

#### Limitations

- Occupy at least one routing layer, costly.

- Could be easily bypassed by the FIB with high aspect ratio.

- If the shield structure can be reverse engineered, it's vulnerable to reroute attack.

- The shield could be disabled by editing its control circuit.

- Only protects against front-side attacks.

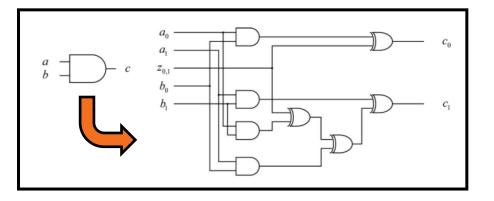

## Analog Shields and t-Private Circuits

#### Limitations

Unreliable due to process variation especially with feature scaling

FLORIDA

Research

#### Limitations

• Large area overhead  $(O(t^2))$

Existing countermeasures are limited and/or expensive

No notion of what is most in need of protection

No approach can be easily incorporated into conventional design flow

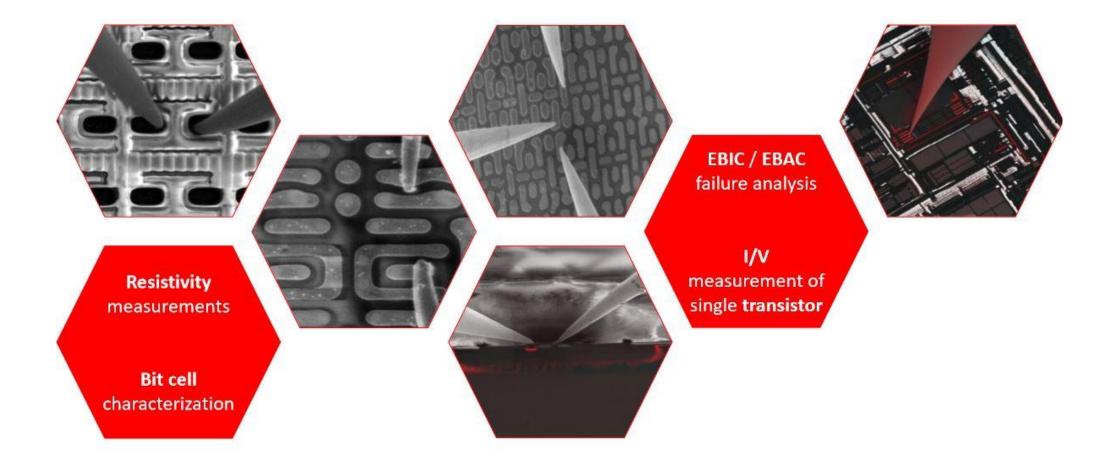

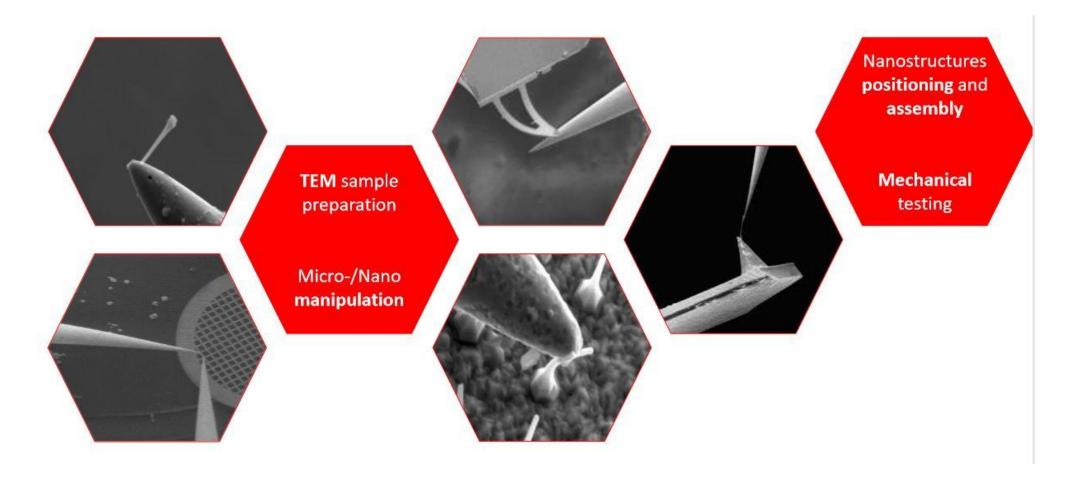

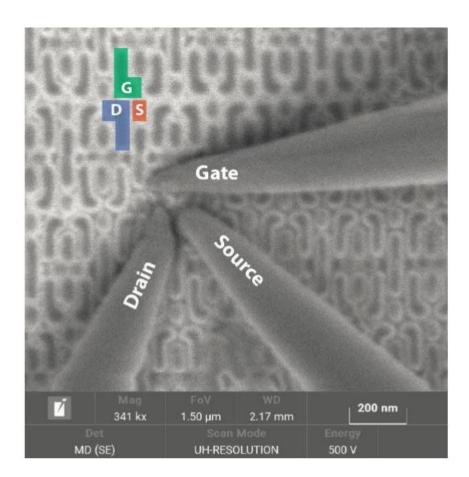

### Applications of Electrical Probing in Semiconductors

1. Nanoprobing and Failure Analysis

UNIVERSITY of **FLORIDA**

### Applications of Electrical Probing in Semiconductors

#### 2. Electrical Characterization

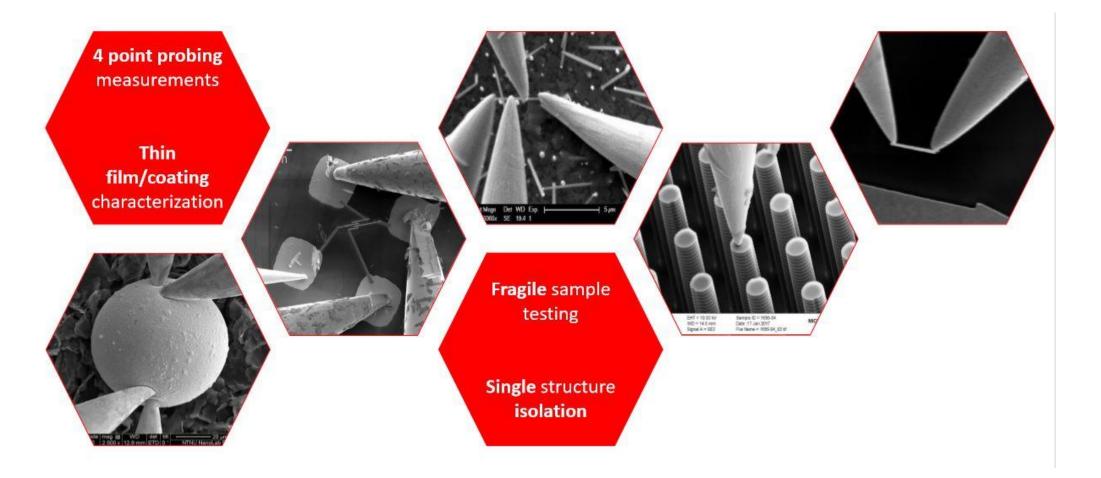

### Applications of Electrical Probing in Semiconductors

#### 3. Sample Handling and Positioning

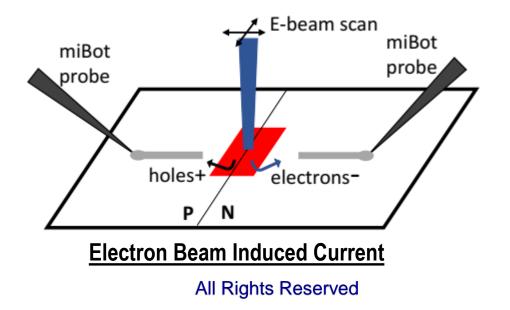

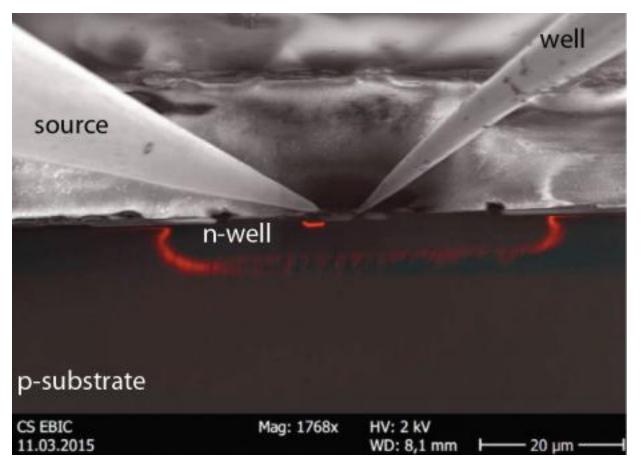

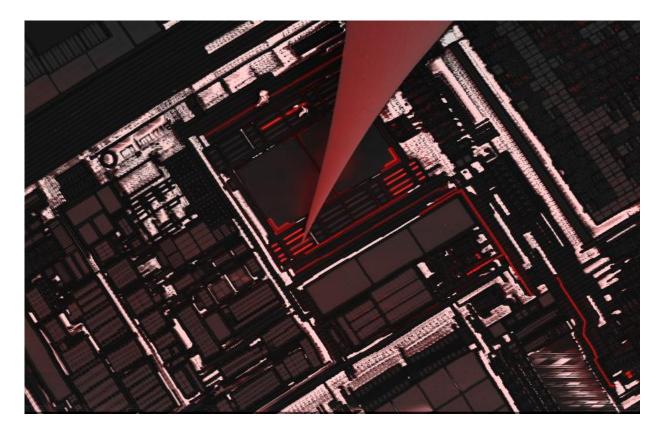

EBIC is a method used for the imaging and characterization of p-n junctions, the recombination strength of defects, and the diffusion length and surface recombination velocity of minority charge carriers in semiconducting materials and devices.

It is most effective when employed alongside EDS or EBSD as part of a wider workflow, for example, nanofabrication in the FIB, or sample preparation for the TEM or atom probe.

#### Map electric fields with the highest spatial resolution

- Visualise internal electric fields from PN junctions or Schottky contacts.

- Validate doping profiles and areas with design, or reverse engineer devices.

- Identify defects with electrical activity and correlate with structure (SE, In-Lens) and composition (EDS, EBSD).

## Applications in Hardware Security

#### Access third dimension with depth profiling.

- Manipulate depth of EBIC signal by changing kV in SEM.

- Investigate EBIC images of cross-sections in FIB-SEM.

- Export EBIC depth series for 3D reconstruction.

## **Applications in Failure Analysis**

#### Map complex electric fields on 3D structures.

- Characterise relationship between surface topography and electrical activity.

- Determine internal quantum efficiency from measured induced- and beam-currents.

- Distinguish between active and passive defects at operating conditions.

#### Enable localisation for TEM or atom probe microscopy.

- Localise defects with sufficient resolution for TEM sample prep.

- Avoid alignment errors by directly imaging defects with EBIC in FIB SEM.

- Use live EBIC imaging to stop milling during sample preparation.

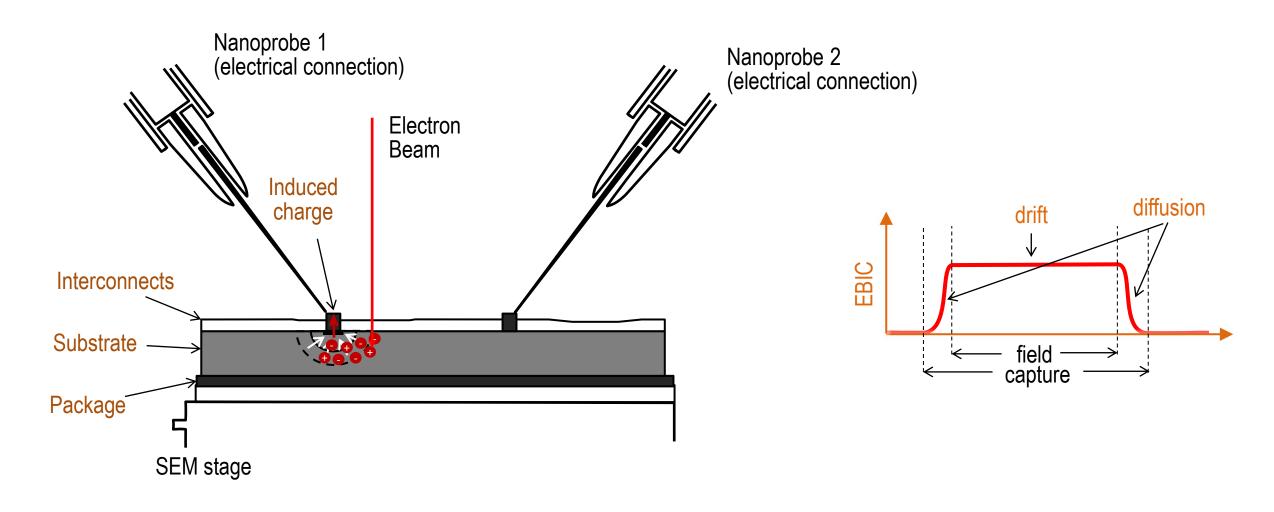

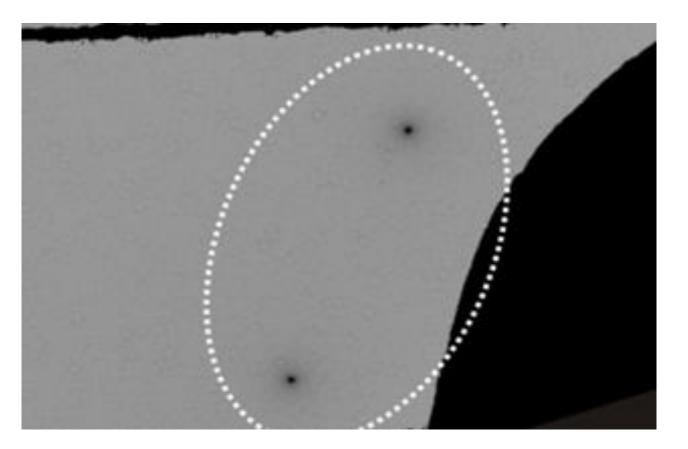

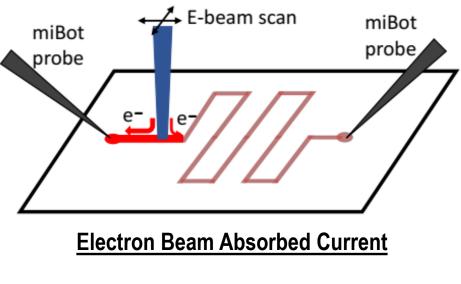

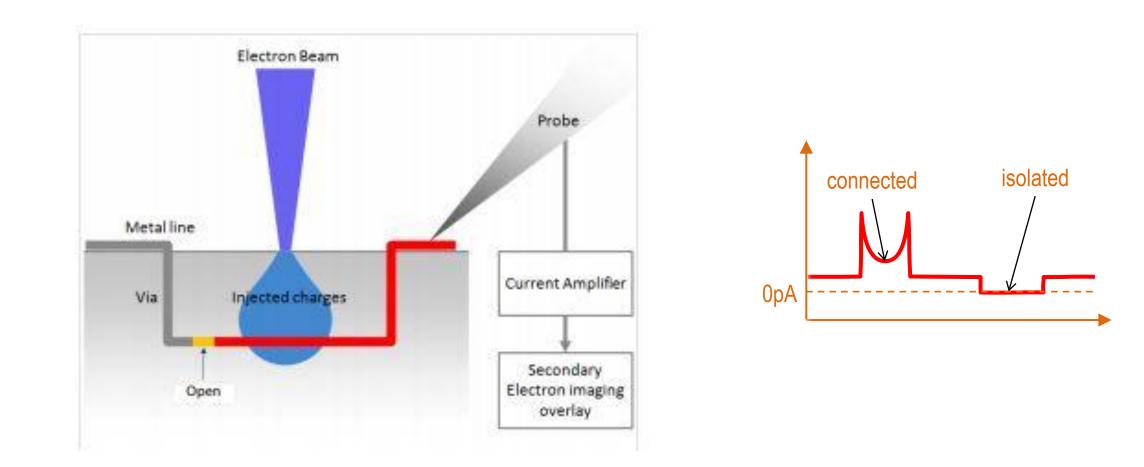

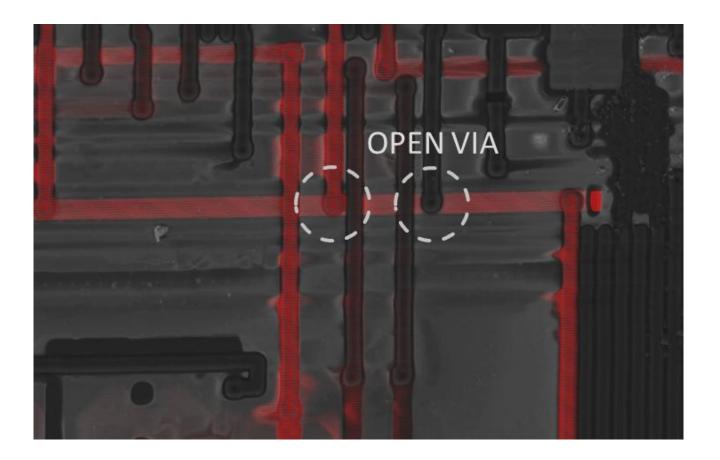

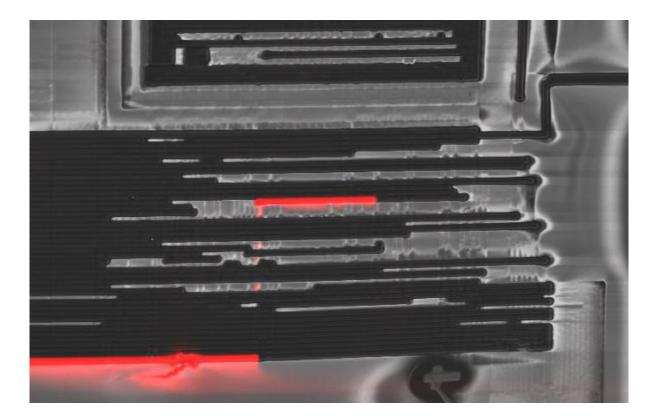

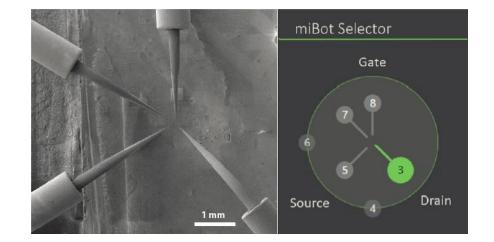

EBAC is a method employed for the identification and physical failure analysis of metal defects (opens and shorts), high resistivity areas and layer non-uniformities in CMOS devices. It is primarily used in combination with electrical nanoprobing.

The electron beam of the SEM scans the DUT and injects charges absorbed by metal lines under the surface. A current is then induced and measured by a probe placed with a miBot nanomanipulator at contact level.

#### Find exact location of any open, resistive or shorting defect.

- Localize cuts caused by cracking, corrosion, electro-migration or particles.

- Identify resistive opens caused by interface contamination at vias.

#### Characterize interconnects with the highest resolution.

- Reveal electrical integrity of nets with sub-micron resolution.

- Diagnose contamination, metal patterning defects, resistive interconnectors.

- Directly isolate defects to exact layer and die location.

#### Access failures invisible in voltage contrast

- Find low resistances that allow charge tunnelling through interconnects.

- Investigate structures in contact with the silicon substrate.

- Characterize large metal structures

### **Applications in Failure Analysis**

#### Localize defects in thin dielectric layers.

- Visualize weaknesses in GOX or COX before breakdown.

- Pinpoint oxide shorts caused by ESD or EOS with sub-micron resolution.

- Preserve the original defect with nW power dissipation during analysis.

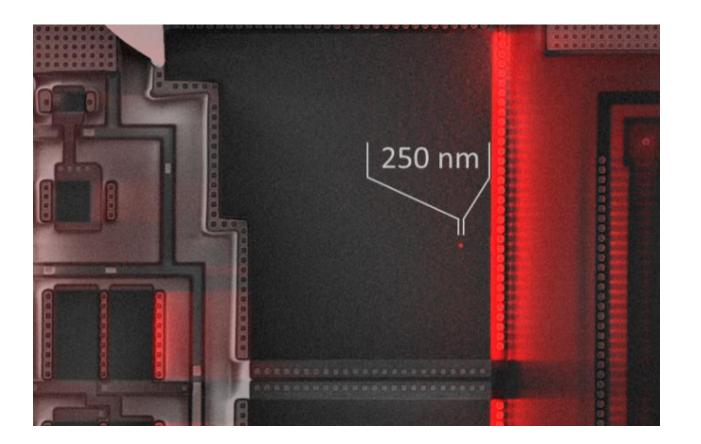

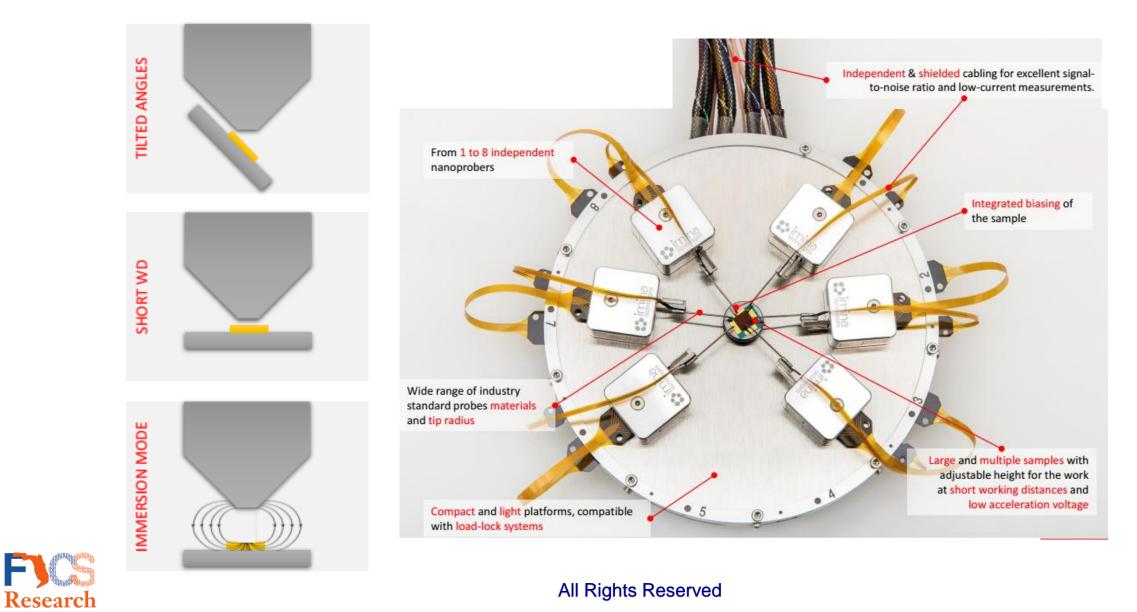

### Needs in the Semiconductor

#### Technologies are shrinking

- Nanometer resolution for a precise positioning

- High mechanical stability for steady electrical contacts

- Adapted probes materials and tip radius.

#### Architectures are becoming complex

- Versatile configuration for a quick adaptation

- Software assistance to guide the operator within the workflow.

#### **Data collection time is limited**

Fast system installation

Reporting capabilities

Research

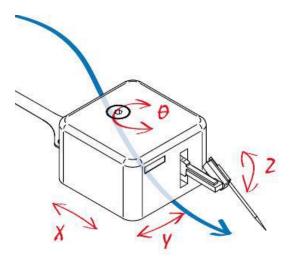

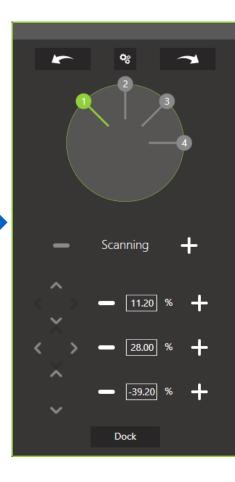

## Core technology: a mobile piezo robot

Axis of movement

- Micro to nanometer positioning resolutions

- Centimeter range displacements

- High mechanical stability and near-zero drift

- Freely moving on their stage. Maintained on it with a magnet

- XYZ and rotation movements

- High vacuum compatible

- Can be adapted to different sample size and applications

### Nanoprobing Platform

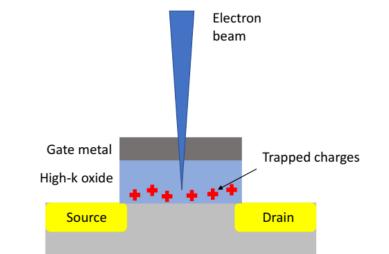

## **Basic Operation Voltage Range**

#### Oxide material sensitive to electron beam:

- Generation of oxide trapped holes.

- Trap generation at the interface.

### Results in:

- Shift of the Threshold voltage.

- Increase of leakage current.

Therefore, it is required to image at low KV to avoid changing transistor characteristics. (typically 500V to 1kV depending on technology).

## Challenges

### Hydrocarbon contamination

- Inside the chamber

- From outside, when installing new probes, sample, etc.

### Contamination has consequences on:

- Imaging quality

- Electrical contact

### Suggestions:

- Store the system in a safe environment.

- Use a plasma cleaner to remove hydrocarbon contamination.

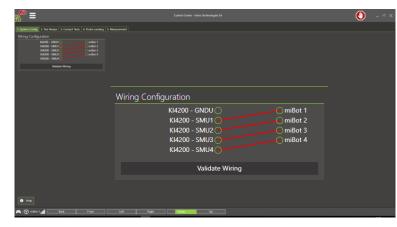

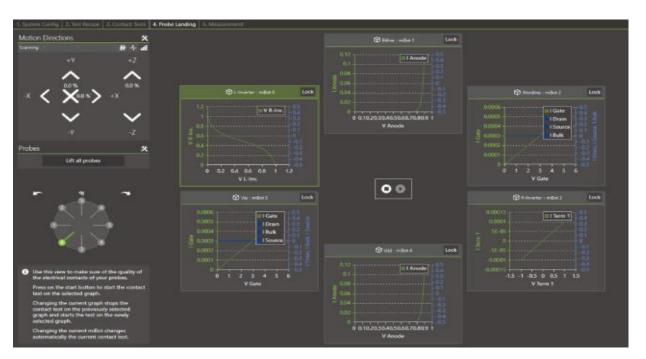

### **Control Center and Probes Approach**

### Steps involved in electrical probing

| st Recipe                         |                                  | DUT- Gate                                                            |                                                                                                                                             |

|-----------------------------------|----------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Select a recipe:                  |                                  | Terminal / Probe: 8 : miBot 8                                        |                                                                                                                                             |

|                                   |                                  | Configure                                                            |                                                                                                                                             |

| Duplicate Recipe<br>Rename Recipe |                                  | Force Measure<br>Step V Voltage: V Gate<br>Start: 0V Voltage: V Gate |                                                                                                                                             |

| Delete Recipe                     |                                  | Step: 0.25V Current: -<br>Points: 5                                  |                                                                                                                                             |

| Graph Definition                  |                                  | Limit: 1E-07A                                                        |                                                                                                                                             |

| Source Settings                   | DUT- Source 🥖                    |                                                                      | DUT- Drain                                                                                                                                  |

| itart Delay (Hold Time) 0 s       | Terminal / Probe: 3 : millot 3 • | Ť.                                                                   | Terminal / Probe: S : millot 5                                                                                                              |

| deasure Delay (Delay Time) 0 s    | Configure                        |                                                                      | Configure                                                                                                                                   |

| Integration Time Normal 👻         | Forse Measure<br>Common: 0V      |                                                                      | Force Measure<br>Sweep V<br>Type: Linear Voltage: V Drain<br>Stat: 0V<br>Stop: 1V Current: I Drain<br>Step: 0.02V Range: Auto<br>Points: 51 |

1: System configuration

2: Test Recipe

#### 3: Probe Landing

#### 5: Measurement & Report

4: Live Contact Testing

### Steps involved in electrical probing

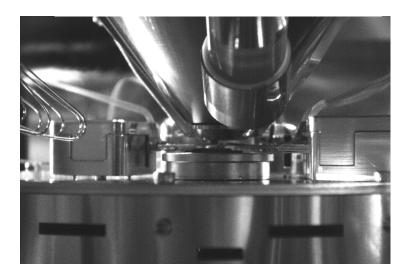

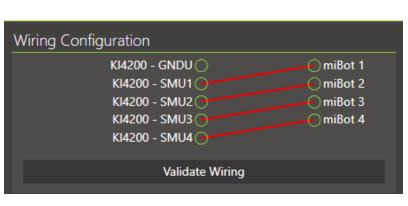

#### 1: System configuration

UNIVERSITY of **FLORIDA**

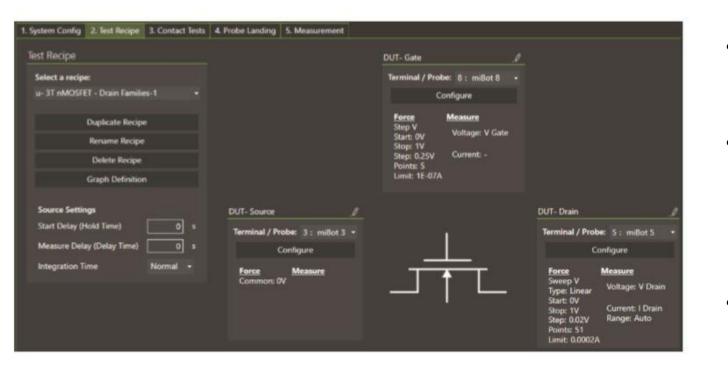

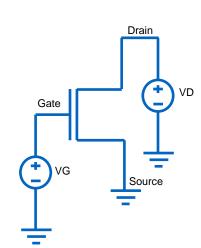

#### 2: Test Recipe

- Predefined test recipes for NMOS and PMOS transistor characterization can be selected.

- Their parameters such as the current compliance, current and voltage range, and number of test points are tuned based on the theoretical properties of the DUT ( Device under Test).

- The device used in this case is 3T-nMOSFET.

### Steps involved in electrical probing

#### 3: Probe Landing

Researc

- The probes tips are then sequentially lowered down in contact with each transistor node.

- Switching from one prober to another and adjusting their speed and positioning step size was intuitively done using the control pad.

- Once all probes had touched down, the beam was deflected away from the test area to avoid affecting electrical measurements.

#### 4: Live Contact Testing

- Precisio<sup>™</sup> contact test module was then used to quickly check the quality of electrical contacts by repeating fast measurements.

- When required, probes position was slightly adjusted until measured curves become characteristic of the DUT.

### Steps involved in electrical probing

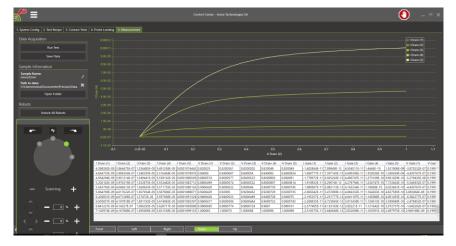

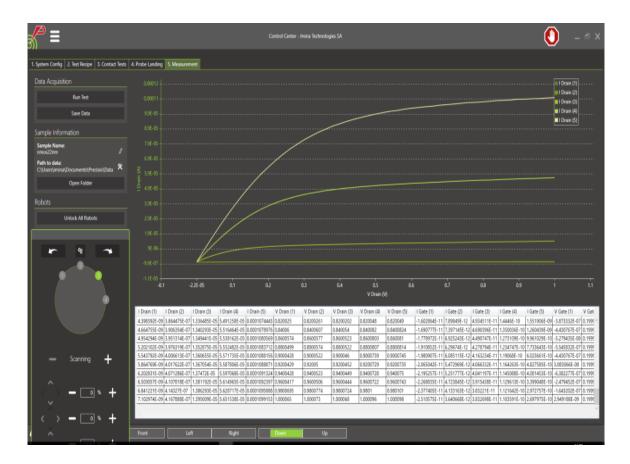

#### 5: Measurement & Report

Research

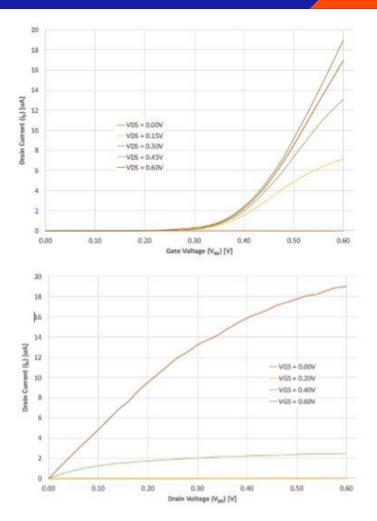

NMOS transistor characteristics (Top) Drain current vs Gate-Source voltage sweep (Bottom) Drain current vs Drain-Source voltage sweep.

#### 5: Measurement & Report

- Before starting the characterization of transistors, leakage current of each channel was measured when probes were not in contact with the DUT. It was lower than 200 fA on all channels.

- The test recipes for this device were configured with a current compliance on ID and IS set to 100 mA. The Drain and Gate voltage sweeps were made in 31 steps of 0.02 V. The Drain and Gate voltage bias were made in 4 steps of 0.20 V.

- The transistors were characterized by measuring the Drain current ID when sweeping Drain-Source voltage VDS at different Gate-Source voltages VGS (ID=f(VDS)) and when sweeping Gate-Source voltage VGS for different Drain-Source voltages VDS (ID=f(VGS)).

- Source current IS and Gate current IG are also measured.